Eliane Annater Email Addresses

Eliane Annater's Work Experience

Najasom Som

Assist. Financeiro

October 2014 to February 2015

Konar Ar Condicionado

Assist. de Compras

June 2012 to September 2014

Edig-O Instalações e Comercio Ltda

Compradora

August 2010 to May 2012

Uptec Construção e Tecnologia

Compradora

September 2008 to July 2010

Show more

Show less

Eliane Annater's Education

UNISA

January 2011 to January 2012

Faculdade Pitágoras

January 2006 to January 2009

UNIP - Universidade Paulista

January 2003 to January 2005

UNISA

January 2011 to January 2012

Faculdade Pitágoras

January 2006 to January 2009

UNIP - Universidade Paulista

January 2003 to January 2005

Show more

Show less

Frequently Asked Questions about Eliane Annater

What is Eliane Annater email address?

Email Eliane Annater at [email protected], [email protected] and [email protected]. This email is the most updated Eliane Annater's email found in 2024.

How to contact Eliane Annater?

To contact Eliane Annater send an email to [email protected], [email protected] or [email protected].

What company does Eliane Annater work for?

Eliane Annater works for Uptec - Construcao E Tecnologia

What is Eliane Annater's role at Uptec - Construcao E Tecnologia?

Eliane Annater is Compradora

What is Eliane Annater's Phone Number?

Eliane Annater's phone (**) *** *** 927

What industry does Eliane Annater work in?

Eliane Annater works in the Construction industry.

Eliane Annater Email Addresses

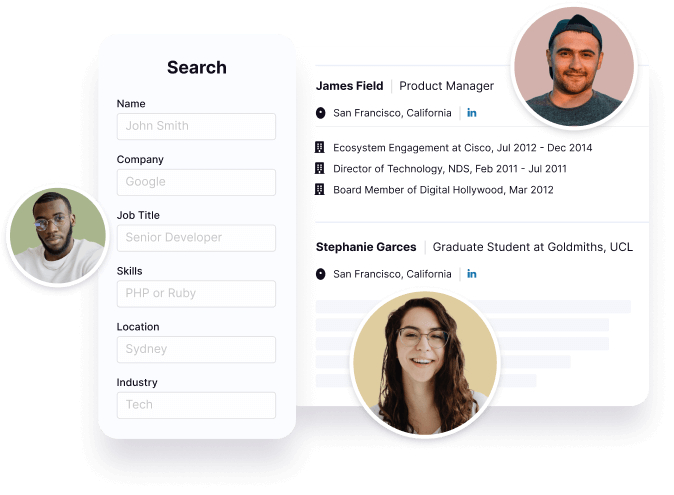

Find emails and phone numbers for 300M professionals.

Search by name, job titles, seniority, skills, location, company name, industry, company size, revenue, and other 20+ data points to reach the right people you need. Get triple-verified contact details in one-click.In a nutshell

Eliane Annater's Personality Type

Extraversion (E), Intuition (N), Feeling (F), Judging (J)

Average Tenure

2 year(s), 0 month(s)

Eliane Annater's Willingness to Change Jobs

Unlikely

Likely

Open to opportunity?

There's 96% chance that Eliane Annater is seeking for new opportunities

Eliane Annater's Social Media Links

/in/eliane-annater-57712228