Dr. John M. Mitchell [Γιάννης]'s Email & Phone Number

Executive Director / Principal Scientist

Dr. John M. Mitchell [Γιάννης] Email Addresses

Dr. John M. Mitchell [Γιάννης] Phone Numbers

Dr. John M. Mitchell [Γιάννης]'s Work Experience

NSF Health Sciences / Pharmalytica

Director / Consultant

January 2009 to Present

Preferred Pharma/OTC Consulting Associates (PPOCA)

Principal Scientist / Executive Director

January 2007 to January 2019

EP Technologies LLC (a GOJO company)

Prinicpal Consultant Nonclincial/Clinical/Regulatory

January 2016 to January 2018

Kinexum Services

Sr Biomedical Scientist / Consultant

January 2007 to January 2012

Akela Pharma / PharmaForm

Senior Consultant DSE / Regulatory

January 2007 to January 2008

Hurley Consulting Associates

Executive Director R&D

January 2006 to January 2007

Purdue Pharma / Mundipharma / Napp

Director

January 1998 to January 2006

Carter Wallace

Senior Director of Regulatory Biology

January 1997 to January 1998

Forest Laboratories

Senior Director

January 1996 to January 1997

MB Research Laboratories

Senior Director of Research

January 1993 to January 1996

Huntingdon LS (previously Bio/dynamics/Pharmaco LSR)

Senior Director

January 1988 to January 1993

Revlon, Inc.

Senior Director Regulatory Affairs/Toxicology

January 1983 to January 1988

General Foods Corp

Director of Biology

January 1978 to January 1982

Senior Reserach Investigator

January 1973 to January 1977

Show more

Show less

Dr. John M. Mitchell [Γιάννης]'s Education

Rutgers University

New York Medical College

The University of Connecticut

Show more

Show less

Frequently Asked Questions about Dr. John M. Mitchell [Γιάννης]

What is John M Mitchell email address?

Email John M Mitchell at [email protected] and [email protected]. This email is the most updated John M Mitchell's email found in 2024.

How to contact John M Mitchell?

To contact John M Mitchell send an email to [email protected] or [email protected].

What company does Dr. John M. Mitchell [Γιάννης] work for?

Dr. John M. Mitchell [Γιάννης] works for NSF Health Sciences / Pharmalytica

What is Dr. John M. Mitchell [Γιάννης]'s role at NSF Health Sciences / Pharmalytica?

Dr. John M. Mitchell [Γιάννης] is Director / Consultant

What is Dr. John M. Mitchell [Γιάννης]'s Phone Number?

Dr. John M. Mitchell [Γιάννης]'s phone (201) ***-*216

What industry does Dr. John M. Mitchell [Γιάννης] work in?

Dr. John M. Mitchell [Γιάννης] works in the Pharmaceuticals industry.

Dr. John M. Mitchell [Γιάννης] Email Addresses

Dr. John M. Mitchell [Γιάννης] Phone Numbers

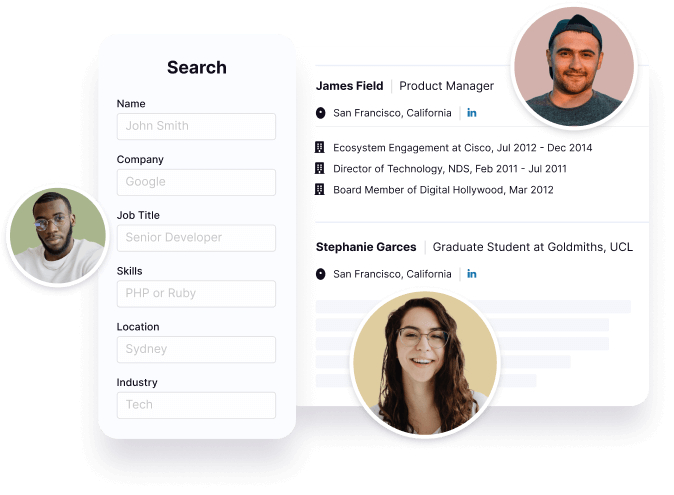

Find emails and phone numbers for 300M professionals.

Search by name, job titles, seniority, skills, location, company name, industry, company size, revenue, and other 20+ data points to reach the right people you need. Get triple-verified contact details in one-click.In a nutshell

Dr. John M. Mitchell [Γιάννης]'s Ranking

Ranked #205 out of 4,101 for Director / Consultant in New Jersey

Dr. John M. Mitchell [Γιάννης]'s Personality Type

Extraversion (E), Intuition (N), Feeling (F), Judging (J)

Average Tenure

2 year(s), 0 month(s)

Dr. John M. Mitchell [Γιάννης]'s Willingness to Change Jobs

Unlikely

Likely

Open to opportunity?

There's 77% chance that Dr. John M. Mitchell [Γιάννης] is seeking for new opportunities

Dr. John M. Mitchell [Γιάννης]'s Social Media Links

/in/dr-john-m-mitchell-γιάννης-69b3937