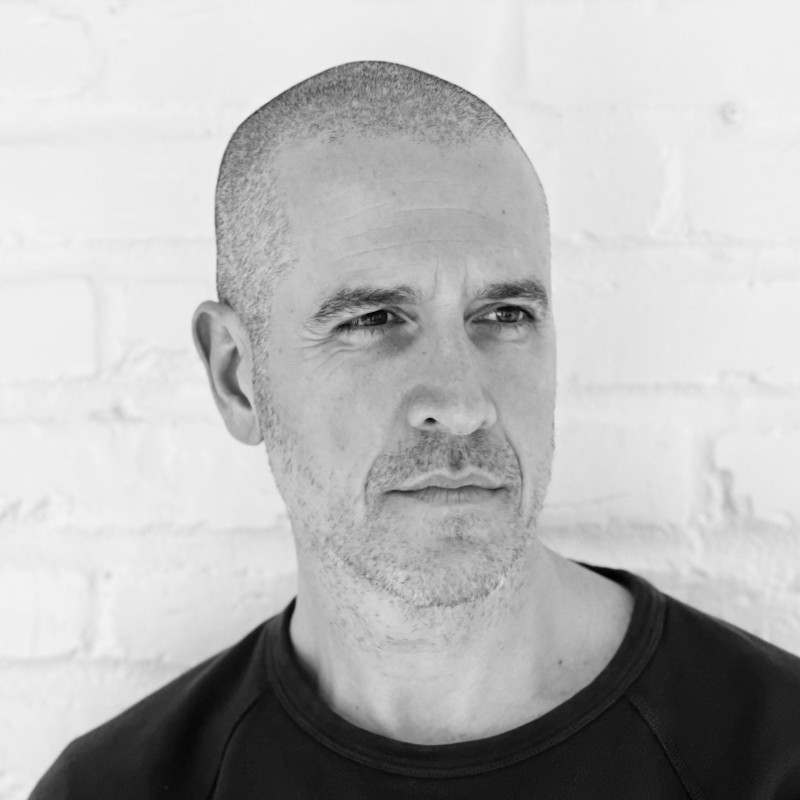

Stephen Bishop's Email & Phone Number

American singer-songwriter and actor

Stephen Bishop's Email Addresses

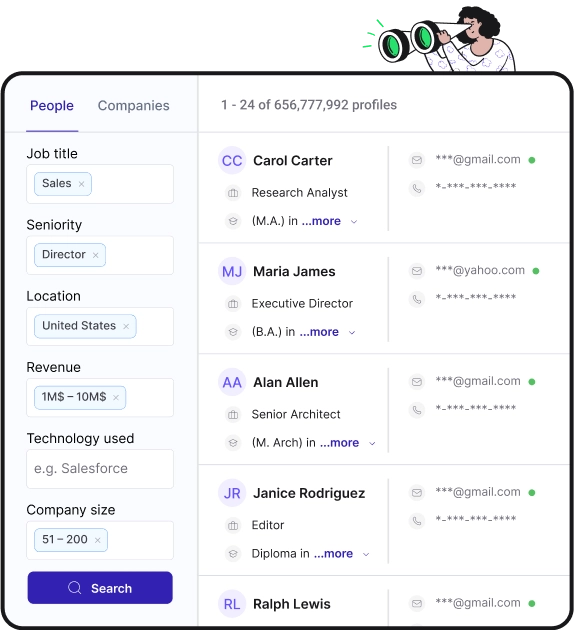

Find personal and work emails for over 300M professionals

Not the Stephen Bishop you were looking for? Continue your search below:About Stephen Bishop

📖 Summary

Stephen Bishop is an extraordinary talent who has mesmerized audiences worldwide with his soulful voice, captivating songwriting, and versatility as an actor. This American singer-songwriter and actor has left an indelible mark on the music industry with his heartfelt ballads and unforgettable melodies. With a career spanning several decades, Bishop continues to captivate audiences with his unique blend of pop, folk, and jazz.

Born on November 14, 1951, in San Diego, California, Stephen Bishop discovered his passion for music at a young age. Influenced by legendary artists like The Beatles and Bob Dylan, Bishop began writing his own songs and honing his skills as a guitarist. His melodic sensibility and introspective lyrics set him apart from his contemporaries, allowing him to carve a niche for himself in the music industry.

Bishop's breakthrough came in 1976 with the release of his debut album, "Careless." The album's lead single, "On and On," became an instant hit, reaching number 11 on the Billboard charts. The song's mellow, soothing melody and Bishop's tender vocals resonated with audiences, establishing him as a formidable force in the world of soft rock. Bishop's music often delves into themes of love, heartbreak, and the complexities of human relationships, striking an emotional chord with listeners.

Over the years, Bishop's songwriting prowess has earned him numerous accolades and collaborations with renowned artists. His song "Separate Lives," performed as a duet with Phil Collins for the film "White Nights," garnered an Academy Award nomination for Best Original Song. Other popular tracks include "Save It for a Rainy Day" and "Something New In My Life." Bishop's contributions to the soundtracks of several films, including "Tootsie" and "Animal House," further cemented his status as a sought-after songwriter.

In addition to his musical talents, Bishop's acting skills have also shone through on both the small and big screens. He appeared in the 1978 cult classic film "National Lampoon's Animal House," showcasing his natural charisma and comedic timing. Bishop's acting career gained momentum with roles in other films such as "The Blues Brothers" and "The Kentucky Fried Movie." His ability to seamlessly transition between various artistic mediums illustrates his versatility as an entertainer.

Despite the many achievements and critical acclaim, Bishop has remained grounded and true to his craft. His introspective nature is reflected in the intimate and authentic connection he establishes with his audience. Whether performing live or recording in the studio, Bishop's rich vocals and poignant songwriting continue to resonate with listeners of all generations.

Through the years, Bishop's music has evolved and adapted to the changing landscape of the industry, but he has always remained true to his signature sound. His body of work reflects an artist deeply committed to honing his craft and delivering masterful compositions that endure the test of time. Bishop's ability to craft beautiful melodies and lyrics that stir the soul is a testament to his undeniable talent and love for his art.

In a world that often prioritizes instant gratification and fleeting trends, Stephen Bishop's music stands as a poignant reminder of the power of timeless art. With each note and lyric, Bishop invites his audience on a journey of self-reflection and emotional exploration. His music has the unique ability to transport listeners to a place of honesty and vulnerability, providing solace and comfort in the midst of life's challenges.

Stephen Bishop's legacy as a singer-songwriter and actor continues to grow, and his music remains a testament to the enduring power of poignant storytelling and captivating melodies. With his soothing voice and heartfelt compositions, Bishop has solidified his place among the greatest artists of his generation. Whether performing on stage, writing a new song, or captivating audiences with his screen presence, Bishop's dedication to his craft shines through, making him an irreplaceable figure in the world of music and entertainment.

Frequently Asked Questions about Stephen Bishop

What is Stephen Bishop's biggest hit?

Earl Stephen Bishop (born November 14, 1951) is an American singer-songwriter, actor, and guitarist. His biggest hits include "On and On", "It Might Be You" and "Save It for a Rainy Day".

What happened to Stephen Bishop?

Since March 2020, Bishop writes, he has undergone nearly a dozen health travails. They began with a late-night fall in his bathtub while sleepwalking, resulting in a hospital visit and 10 stitches in his head. A few weeks later, a medication he was taking toxified in his system.

What year did Stephen Bishop come out?

Born in San Diego, Bishop burst onto the scene after signing to the ABC label, with the outstanding album Careless, released late in 1976.

What was Stephen Bishop's greatest discovery?

Popular cave areas such as the Mammoth Dome and the Ruins of Karnak are credited as having been discovered by Bishop. In 1842, during a visit to the Croghan estate, Locust Grove, in Louisville, Kentucky, Bishop drew a map from memory of the explored passageways of the cave.

Stephen Bishop's Email Addresses

People you may be

interested in

Entrepreneur

American voice actor and animator

Indian actress

American businesswoman and actress

American basketball player

Football wide receiver

American singer-songwriter and actress

American actor and DJ

American media personality

American businessman and television producer

American actress

YouTuber