Rajath Narasimha's Email & Phone Number

System Verification Engineer at Cadence Design Systems

Rajath Narasimha Email Addresses

Rajath Narasimha's Work Experience

Tensorcom

RF/Analog Characterization Engineer

November 2014 to December 2015

Tensorcom

Product Engineer - RF/Analog Validation Group

November 2014 to December 2015

Qualcomm

RF/Analog Product Development Engineer

December 2012 to November 2014

Qualcomm

Product Engineer - RF/Analog Validation Group

December 2012 to November 2014

Ampere Technology

Undergraduate Intern/Hardware Design Intern

January 2010 to June 2010

Ampere Technology

Hardware Design Intern

January 2010 to June 2010

Show more

Show less

Rajath Narasimha's Education

Product School

January 2021 to January 2021

University of California, Berkeley

January 2019 to January 2020

San Francisco State University

January 2010 to January 2012

Visvesvaraya Technological University

January 2006 to January 2010

Sri Bhagawan Mahaveer Jain College

January 2004 to January 2006

Coleman University

January 2015 to January 2016

Sri Aurobindo Memorial School - India

January 2002 to January 2004

University of California, Berkeley

January 2019 to January 2020

Coleman University

January 2015 to January 2016

San Francisco State University

January 2010 to January 2012

Visvesvaraya Technological University

January 2006 to January 2010

Product School

January 2021 to January 2021

University of California, Berkeley

January 2019 to January 2020

Coleman College

January 2015 to January 2016

San Francisco State University

January 2010 to January 2012

Visvesvaraya Technological University

January 2006 to January 2010

Show more

Show less

Frequently Asked Questions about Rajath Narasimha

What company does Rajath Narasimha work for?

Rajath Narasimha works for Cadence Design Systems

What is Rajath Narasimha's role at Cadence Design Systems?

Rajath Narasimha is Product Lead - System Verification Group

What is Rajath Narasimha's personal email address?

Rajath Narasimha's personal email address is r****[email protected]

What is Rajath Narasimha's business email address?

Rajath Narasimha's business email address is rajath.narasimha@***.***

What is Rajath Narasimha's Phone Number?

Rajath Narasimha's phone (**) *** *** 240

What industry does Rajath Narasimha work in?

Rajath Narasimha works in the Semiconductors industry.

Rajath Narasimha's Professional Skills Radar Chart

Based on our findings, Rajath Narasimha is ...

What's on Rajath Narasimha's mind?

Based on our findings, Rajath Narasimha is ...

Rajath Narasimha's Estimated Salary Range

Rajath Narasimha Email Addresses

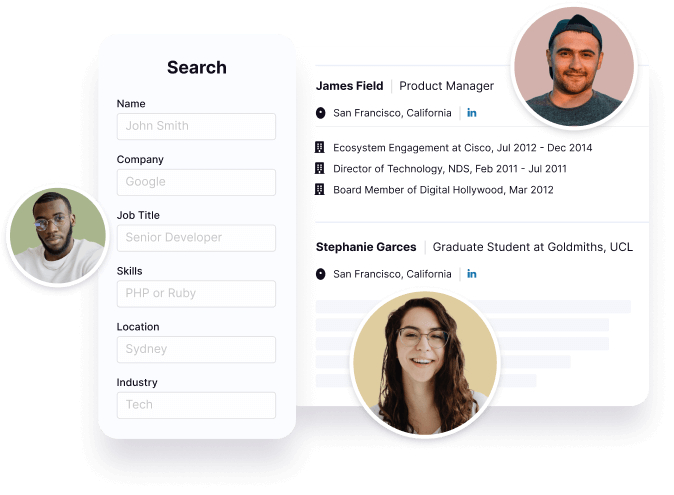

Find emails and phone numbers for 300M professionals.

Search by name, job titles, seniority, skills, location, company name, industry, company size, revenue, and other 20+ data points to reach the right people you need. Get triple-verified contact details in one-click.In a nutshell

Rajath Narasimha's Personality Type

Introversion (I), Intuition (N), Thinking (T), Judging (J)

Average Tenure

2 year(s), 0 month(s)

Rajath Narasimha's Willingness to Change Jobs

Unlikely

Likely

Open to opportunity?

There's 89% chance that Rajath Narasimha is seeking for new opportunities

Top Searched People

American singer-songwriter and musician

British journalist and television presenter

American actor and filmmaker

Canadian singer

American actor and filmmaker

Rajath Narasimha's Social Media Links

/in/rajathnarasimha /company/cadence-design-systems /school/uc-berkeley/